- +1

3D封装全解析:概念、设计与前景展望

原创 赵莹 远川科技评论

作者:赵莹

编辑:易俊江、杨健楷

4月27日晚8点,远川研究所邀请到了UCIe标准联盟里两家重要EDA公司的技术专家,新思科技中国区副总经理朱勇先生,和芯和半导体联合创始人、高级工程副总裁代文亮博士做客直播间,与各位观众一起探讨交流“Chiplet大热背后,3D封装如何抢占芯片产业制高点?”这一行业热点。

在直播中,两位嘉宾认为:

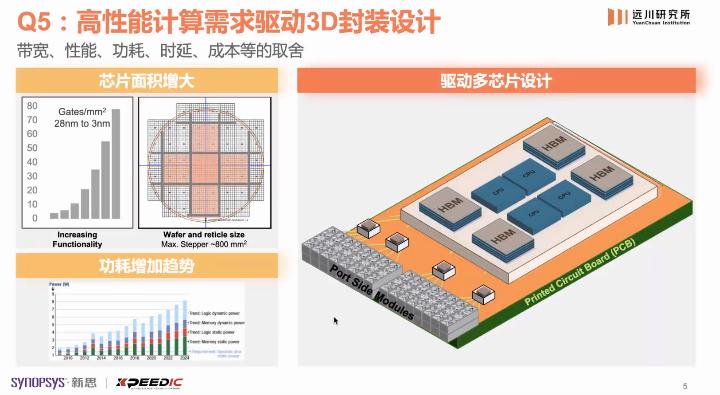

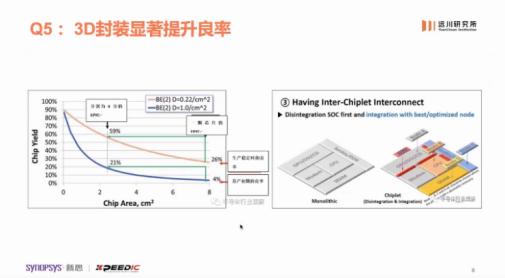

1. 3D封装是必然的发展趋势。首先,随着芯片越来越复杂,芯片面积、良率和复杂工艺的矛盾难以调和,到一定程度就必须把大的芯片拆解成一些小的芯片。其次,3D封装可以通过采用成熟工艺去实现一些不需要用到最先进工艺的功能模块,从而降低成本。

2. 在3D封装领域,晶圆厂和封装厂都有各自的优势,这是一块高地,大家可以协同共进。

3. 3D IC未来在中国将呈现爆发式的增长,从需求来看,这也是一个必然的趋势。对性能有极致追求的应用,势必要用Chiplet或者3D IC的解决方案。但应注意,这一趋势的前提是,做大芯片的难度或者良率成本,超过通过Chiplet集成的成本。

以下,为精简后的直播问答记录,直播全程回看,请移步“远川研究”APP。

01

重塑芯片架构的3D封装

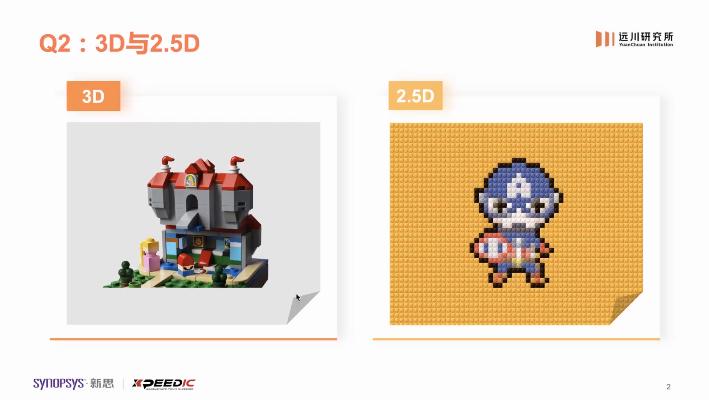

远川:如何理解3D封装的概念?2.5D、3D、Chiplet等名词如何理解?

朱勇:简而言之,3D封装就是将一颗原来需要一次性流片的大芯片,改为若干颗小面积的芯片,然后通过先进的封装工艺,即硅片层面的封装,将这些小面积的芯片组装成一颗大芯片,从而实现大芯片的的功能和性能。这种小面积的芯片就是Chiplet,一般翻译成小芯片或芯粒。

2.5D是在二维的平面上,基于硅中介层(Interposer),将Chiplet组成一个大的芯片。Chiplet之间在硅中介层上通过数据的交互,形成一个系统级的芯片。而3D则是在三维空间组装芯片,在垂直的方向堆叠更多的小芯片,从而集成更多的功能。

举个例子,如果要一次性做出一个比较大的乐高模型会有一定难度。我们可以把大的乐高积木拆分成一个个小颗粒,从平面和立体的维度分别把这些小颗粒在乐高的基板上堆叠起来,从而组装成理想的大模型。这就是3D封装的概念。

代文亮: SoC把所有的功能放在一个大芯片上,规模越做越大,芯片面积也越来越大,良率、工艺都会碰到一些问题。这种情况下自然而然就会想到将不同工艺、不同小芯片,集成到一个小封装里。但集成的时候也会遇到问题,例如放在封装基板上,也就是平铺Side by Side的方式,互连会有瓶颈,间距(Pitch)也可能不够。

所以就要采用硅中介层的方式来集成,这就是我们常说的2.5D。如果再垂直堆叠的话,就是3D,也就是从平房往楼房的方向来做。

远川:3D封装,听起来是个封装的概念,但实际中我们看到台积电、三星这样的晶圆厂也做了很多3D封装,这是为什么?中国的封装厂规模已经很大了,他们在3D封装领域会有机会么?

代文亮: Chiplet、3D、2.5D,归根结底是芯片和芯片堆叠,大家自然而然想到是封装厂来做、还是Foundry厂来做。

Foundry厂有自身的优势,不管是数字芯片还是模拟芯片都是在自己的工艺上跑的,很方便做后期的封装集成。封装厂说其实这个也是我的强项,芯片怎么摆放、硅中介层怎么设计,也是封装厂可以做的。所以,Foundry厂比如台积电、三星,封装厂比如ASE、矽品,都在做3D封装。这就形成了一块高地, Foundry厂和封装厂都想做这件事。

大陆的 Foundry厂都实现了大规模量产,比如中芯国际、华虹、华力。大陆封装厂在全球也很厉害,比如长电、天水、通富。我认为二者都是有机会的,在做2.5D和3D IC集成的时候,线宽是微米量级,这种条件下封装厂也搞得定。所以我认为不只是Foundry厂或者只是封装厂有机会,而是大家都有机会,未来可以协同来做。

远川:最近AMD收购了赛灵思,在AMD高歌猛进的背后,3D封装发挥了很大的作用,2015年发布的采用HBM(High Bandwidth Memory)的GPU是一个很好的案例。我们怎么从3D封装的角度来理解AMD的案例?

朱勇:十几年前,赛灵思做28nm的7V2000T FPGA的时候就采用了台积电的2.5D技术,以完成多Die芯片层面的封装。AMD此前推出的EPYC(霄龙)处理器系列,近几年通过Chiplet技术和先进封装技术实现了质的飞跃,扩大了在数据中心的市场份额。

AMD的霄龙处理器系列通过不同的工艺集成了一个io Die和4-8颗的CPU Die,很好地展示了Chiplet的优势。io Die采用了成熟工艺,比如14nm;而 CPU则采用最新的7nm工艺,通过集成不同的工艺大幅提高了芯片的良率。

不久前,AMD推出了集成3D V-cache技术的第三代霄龙产品,再次展示了3D IC先进封装工艺带来的优点,把处理器的性能再度提升了一个台阶。第三代霄龙处理器在每一个 CPU Die上都集成了额外的Level 3 的缓存(Cache),整体缓存容量超过700 MB,这一点是非常惊艳的。新思科技在与AMD的合作中,采用了AMD最新的处理器进行测试,VCS验证效率实现了66%以上的性能提升。此外,我们也通过一些客户了解到,采用 AMD最新3D IC封装的芯片,打游戏的体验也有质的飞跃。

除了AMD,英特尔也在往这方面努力。英特尔去年推出了一颗较为复杂的芯片Ponte Vecchio,通过5种不同的工艺将超过1000亿个晶体管、47颗小芯片集成到一颗大芯片上。这两家公司都通过采用Chiplet和先进封装的技术,推出了更强更优的处理器方案。

远川:接下来请代博士介绍一下具体的3D封装的结构图。

代文亮:首先看中间这张图。在传统的GDDR5设计中,OFF Chip Memory、Silicon Die通过封装基板或者PCB板连起来,走的路径相对来说比较长。,右边的图是通过HBM宽带存储颗粒来实现,HBM宽带存储颗粒跟中间紫色的,GPU/CPU,还有一些AI芯片,可以用作存储交换。

按照最早的一个做法,是大家各自包,包了以后,再放到 PCB板上,后来又进一步说能不能放到封装基板上。但这里面就有一些问题,封装基板上晶圆是切成小颗的,还要封装基板包一下,再贴到PCB板,这样连的就太远了。

从这个角度就回到最左边的图,HBM通过 TSV Microbump,TSV也就是Through -Silicon-Via,穿过硅衬底。硅衬底以前只是做个托盘,里面没有任何的走线或者电路,属于是x往y方向走,现在要往z方向走,往上、往下走,这样的话就必须要有个东西来打通,Through -Silicon-Via就是穿过硅衬底。

层与层之间,HBM的Die和下面的Die,实际上是通过微凸块(Microbump),一直往上堆,可以堆好多层,堆了以后看到的绿色的一块就是Logic Die,橙色的部分就是HBM颗粒,实际上是一个Stack Die的堆叠裸片。

再往右边是高速的io、GPU、CPU或者SoC的Die,里面有个问题:紫色跟绿色怎么能连得通?实际上这些速度都是很快的,另外因为CPU、 GPU、 SoC Die基本上采用先进节点做, Pitch间距都比较小,这种要通过RDL把它拉通。

这是左右xy方向上,另外还有TSV往下的方向,实际上还要把所有东西集成到封装基板上,所以下面有个Interposer硅载板,它实际上也是一颗芯片,只是这个芯片是不含有晶体管的。

远川:3D封装是怎么流行起来的?

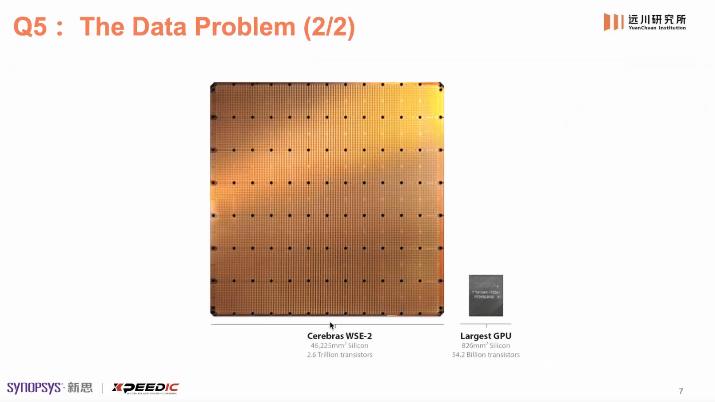

朱勇:如今芯片越来越复杂,需要集成的功能越来越多,面积也越做越大,这导致初期芯片的良率不会很高,利润有限。从良率的角度和工艺复杂的角度,这是必然的矛盾,当它发展到了一定程度就必须要把大的芯片拆解成一些小的芯片。

从性价比的角度来看,采用成熟工艺来完成一些不需要用最先进工艺的功能模块,然后把不同工艺的芯片封装在一起达到大芯片的效果,一定是最优解。我认为这也是目前 Chiplet和3D IC越来越流行的主要原因。

代文亮:我可以补充一点,基于成本的考虑,存储芯片就像刚才提的HBM不可能用3纳米5纳米来做,需要采用不同工艺。所以工艺越先进的时候,越需要走3DIC这条路。逻辑可以到3nm、2nm,但是模拟、存储,不可能用先进工艺做,成本角度来看是不划算的,这种情况下就导致3DIC先进封装是一个必然的趋势。

Cerebras公司推出的大芯片

SoC和3D封装不同的良率的对比。

远川:3D封装相对于原来IC基板有什么额外的要求吗?

代文亮:传统的Side by Side的方式,我们叫做SIP(System in Package),通过封装基板进行互连,在精度、线宽间距要求上,比PCB板高一些,要达到 IC level,这两个实际上差距很大。所以刚才提到封装厂去做,并不是采用封装基板来做,这个是做不到的。为什么一定要用硬件方式来做?先进节点里,io pitch间距、线宽间距是非常小的,这在基板里面根本走不出来,但通过硅载板可以很好的实现。这就是2.5D。3DIC就是往上堆,在SIP上是没办法做的,可能对一些低速信号是可以的,但对高速模拟基本上是没法实现的。

02

全流程3D封装设计分析平台

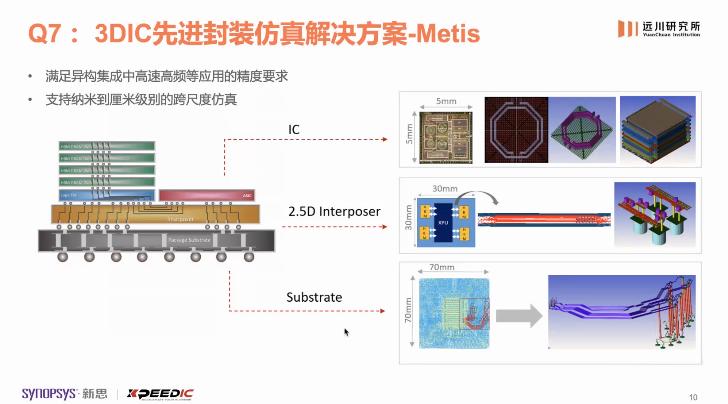

远川:可以说,3D封装是芯片架构的一次革命,那么必然会带来芯片设计上的难题,请两位专家从自己的角度出发,分别阐释一下3D封装给EDA带来的挑战。

朱勇:芯片面积越来越大以后,需要通过3D IC技术把不同的小芯片集成到一起,从设计规划、布局、布线到集成,牵涉到不同的工艺、不同的信号、不同的封装等诸多因素。比如单点工具存在数据之间的交互,会给测试带来很多麻烦。在3D层面,链路有没有通,信号之间有没有串扰,信号和功耗的完整性都是需要提前分析的问题。

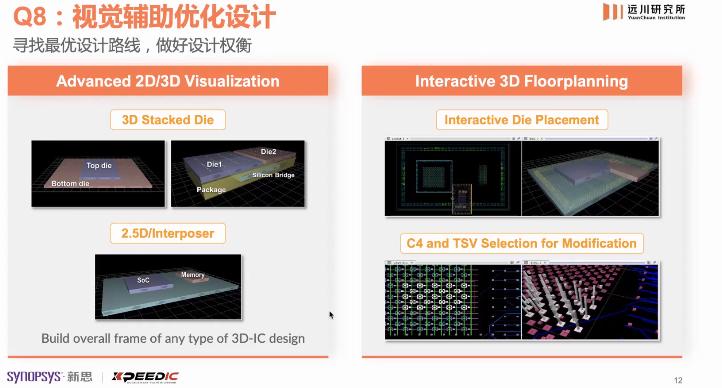

新思科技的3D IC Compiler工具联手芯和链路端的信号分析工具,通过把所有的单点工具都集成起来,为开发者提供一个可视化的设计环境,助力实行我们常说的“Shift left”策略,让开发者能够提前进行各种尝试,以实现更快的收敛和迭代速度。

代文亮:芯片之间是数据在吞吐,也就是获得、处理,再输出,在这个过程中需要较大的带宽,低延时。这个要求就比较高,之前一颗芯片要从封装跑到PCB再跑到另外一颗芯片,现在直接通过Interposer很快就过去了,信号、带宽、延时都会好很多。

好是好,但是问题在哪儿?所有的芯片都挤到一起了,各种芯片之间的耦合到底怎么样?这块要做一些分析,而且难度非常大,我们希望芯和与新思一起开发一套完整的3D封装设计平台,这样不用数据导入导出,可以直接在里面做起来了,提高数据的一致性、可靠性。

远川:为应对这些挑战,两家公司解决了哪些难题?

朱勇:新思科技的3D IC Compiler为开发者提供了采用最新的工艺节点设计芯片的可行性,通过3D IC里集成的编译,开发者可以通过看到一个结果,再去做各种各样的组合,尝试能否满足PPA(Performance Power Area)目标的要求。

新思科技和芯和主要是在信号完整、预热分析方面进行合作。我们把通过3D IC Compiler的设计无缝交接到芯和的工具链上进行分析、处理。从规划、路径的探索,到编译、集成,再到后面的信号分析,能够很快地进行全链路迭代,按照规定的 PPA要求收敛设计。

远川:芯和的设计平台,会着重突出芯片,硅中介和PCB三个层次的联合仿真,芯和为什么会突出联合仿真?针对联合仿真,建模仿真是怎么解决的?

代文亮:其实挑战很大,中间的Interposer硅载板,看起来好像很简单,但是线宽间距都是微米级或者更小。另外一个就是HBM,不能只放几根线,而是要放一组线,比如1024根线,一组线一抽的话规模太大,可能就抽不出来。这种情况就需要比较强有力的工具把差损、串扰、隔离,全部抽出来,最后带到io仿真,所以计算量非常大。

如果 SoC或者io是自己设计的话,需要考虑芯片和芯片间的影响,就是上面和下面的影响。所以信号这一块,一定要支持从纳米尺度到微米尺度到厘米尺度的跨尺度分析,规模会非常大,这种情况就要求一个能够对芯片封装和Interposer都能cover自适应的仿真工具。

既要考虑早期的规划,如何快速高效来评估设计是不是合理。另外还要评估两个芯片之间距离跑多远,不然差损太大了。后期的话就要做整个信号的链路的验证,而且一定要验证较大规模的。所以仿真难度是非常大的,芯和在这块可以给大家提供一个很好的支撑。

远川:3D封装的EDA解决方案会强调全流程,两家公司在推出全流程解决方案的时候,都做了哪些工作?

朱勇:新思科技的 3D IC Compiler将设计的初期规划、布线、布局,以及芯和的仿真分析工具都集成到了一个环节里面。此外,我们还提供了可视化图形界面,让开发者能够更直观地看到采用3D的堆叠或者2.5D的摆放后,信号互联的位置对不对?信号能不能传过去或者有没有干扰和错误?这些都可以在我们的可视化工具中进行交互。

代文亮:我们最关心的就是PPA,从面积上来讲,就是从平房到楼房,想把它做得小。

功耗方面,原来从一颗芯片传到另外一块,从封装到PCB,整个链条很长,功耗要大很多。如果直接采用Interposer,距离会很短,功耗就要好很多。

性能方面,带宽、延时、功耗都有提升。左边灰色的部分是我们需要的,首先有封装(Package),到Die的堆叠(Die Stack),接下来是电源供电(Power Delivery),这一块怎么去处理,然后还有下面的电源网络(Power Grid)。另外还有硅通孔(TSV),包括一些凸块(Bump),到底该打成什么样,一个还是两个,还是合到一起来给信号提供支撑。

右边是仿真验证或者优化。首先是模型(model)进行提取的时候,io和整个3D IC结构的参数提出来以后,做一些分析,包括timing、power、功耗,还有电源完整性分析,及直流的IR Drop。Signal integrity就是信号完整性,因为速度太快了,这种情况下信号完整性、信号质量非常关键。

03

3D封装的发展潜力

远川:请两位专家分别展望一下3D封装在中国的市场前景?

朱勇:我认为,从需求来看,未来几年到几十年的范围里,3D IC在中国市场会呈现爆发式的增长,这是一个必然的趋势。

为了处理越来越大的数据量,芯片需要集成更多的功能。一些通用的芯片无法覆盖所有需求,导致越来越多的应用场景需要使用定制化的芯片,也就是专用领域的特定架构解决方案(Domain Specific Architecture,DSA)。定制芯片需求越来越多,将提高对于更好、性价比更高的技术方案的需求。目前看来,Chiplet和3D IC是一个行之有效的方法,在未来几年到十几年里,客户需求、应用场景都会越来越多。

代文亮:新思、芯和都加入了UCle联盟,我们非常看好3D IC的趋势。另外一方面,中国是硬件之都,实际上都是在PCB板上集成,那么现在是不是有可能把原来一个个Die进行封装的方式,合到一起来走Chiplet的方式,这应该是比较高效可行的,而且节点也不受大限制,所以我认为这是比较好的契机。AMD、英伟达、Amazon、英特尔都在走这条路,我们大陆的客户更需要走这条路。

因为大家是通过编程的方式来实现一些算法,这种情况下程序有bug就要修,每次都去找SoC,周期就很长。如果走Chiplet,把其中一块换掉,效率很快就提高了,周期也比较短,也可以迭代得非常漂亮。另外一方面,这也是对知识产权的一种保护。

现在芯和联合新思在中国大陆做了一个全链路的支撑,一个完整的3D封装设计平台,所以我们有很好的本土支持。我相信国内的Foundry厂和封装厂,现在已经都动起来,在做这件事。

远川:国内的Chiplet市场大概什么时候会爆发?哪些应用会率先落地?

朱勇:对性能有极致追求的应用,势必要用Chiplet或者3D IC的解决方案。对性能有极致追求,意味着要把晶体管的密度做得越来越高,速度越来越快。另外一个是数据处理,数据交互将对带宽、吞吐量和速度提出更高的要求,导致芯片会越来越复杂、越来越大,要求远远超过了目前的工艺节点能够满足的PPA目标和成本,目前看来,在这种场景下就只能采用 Chiplet和3D IC技术。

率先会落地的应用包括了高性能计算HPC、个人用的平板电脑、高性能的 GPU,以及目前在汽车上集成的芯片。传统的 PCB板级的互联数据吞吐量和性能已经满足不了不同功能模块的芯片之间的互动,只能再往上走一层到Interposer层才能满足这个级别的数据吞吐量。

远川:听说台积电的 CoWoS成本非常贵,几乎相当于Die的成本, TSV就更贵了,是否高封装成本会限制Chiplet去扩大应用?

代文亮:有这么一个说法,毕竟Chiplet是比较高端的一个技术,如果芯片的出货量少于100万颗,不太建议走这条路,这是一个硬指标。

朱勇:大家都知道Chiplet、3D IC技术非常先进,但并不是所有的设计都要采用它们。把功能模块切割得太小,从经济效率来说是不合算的。只有当做大芯片的难度或者良率成本,超过了通过Chiplet集成的成本,才会有收益。切割得越小,集成的难度越大,复杂度越高,也将付出更多额外的成本。比如,把原来一颗800平方毫米的芯片切割成4颗200平方毫米的芯片,把它们集成起来一定会产生一些冗余。所以,并不是切割得越细越小就越好,我们需要考虑边际效应。

04

尾声

3月初,英特尔、高通、台积电、三星等十大芯片行业龙头联合成立了Chiplet标准联盟,正式推出通用Chiplet高速互联标准“UCIe”。另一边,苹果在今年的春季发布会上推出M1 Ultra芯片,也采用了类Chiplet技术。

简单来说,Chiplet就是将多个满足特定功能的模块芯片与底层基础芯片封装在一起。但是想要实现芯片之间的联通并不是一件易事,信号完整性及其相互之间的耦合都是问题。面对这样的难题,芯和联合新思推出的3D IC封装设计分析平台主要做了两件事:

一是“shift left”,为开发者提供一个可视化开发的环境,能够提前做各种各样的尝试,达到更快的收敛、迭代。二是联合仿真,着重突出芯片、硅中介和PCB三个层次的联合仿真,支持从纳米尺度到微米尺度到厘米尺度的跨尺度分析。这也使3D IC封装设计分析平台成为推动3D封装潮流的有力武器。

从技术的角度,我们当然期待芯片面积越来越小;而考虑商业角度,性价比才是最重要的。二者并不矛盾, 3D封装同时兼具技术与商业价值,提供了边际效应下的最优解。

可以预见的是,在不远的未来,当“微缩化”难以担当牵引摩尔定律继续前进的重任,采用Chiplet尖端封装技术,即3D封装,的确是摩尔定律的“续命良药”。

如果你从事EDA领域工作,欢迎和远川进行更多交流,我们会组织高质量分享群,并开展线上、线下交流活动,互通有无、提升产业认知。可以添加:Bradenyang0916,并注明姓名、工作单位等。

原标题:《3D封装全解析:概念、设计与前景展望》

本文为澎湃号作者或机构在澎湃新闻上传并发布,仅代表该作者或机构观点,不代表澎湃新闻的观点或立场,澎湃新闻仅提供信息发布平台。申请澎湃号请用电脑访问http://renzheng.thepaper.cn。

- 报料热线: 021-962866

- 报料邮箱: news@thepaper.cn

互联网新闻信息服务许可证:31120170006

增值电信业务经营许可证:沪B2-2017116

© 2014-2024 上海东方报业有限公司